## Lon 总线多点 I/O 智能节点的开发

武汉大学电子信息学院(430072) 黄天戍 祁 昶

摘 要:介绍了智能节点在现场总线控制系统中的重要性,给出了扩展智能节点的 I/O 点数的方法和电路原理图以及采用该智能节点组建的基于 Lonworks 技术的现场总线控制设备的应用实例。

关键词:Lonworks 智能节点 I/O 扩展

Lonworks 现场总线由美国 Echelon 公司于 1993 年推出,由于其开放的网络操作系统、标准的网络通信协议、丰富的介质接口模板、支持多种介质之间相互通信等特点,在工业控制领域得到了广泛响应。目前已有多种支持 Lonworks 技术的芯片, Echelon 公司的神经元芯片 NeuronC3150 是一种集 3 个 8 位 CPU 及网络通信协议(LonTalk 协议)为一体的芯片。采用该芯片构成的智能节点在 Lonworks 现场总线控制网络中起着举足轻重的作用,它能使现场设备之间相互通信,快速地交换信息,以满足系统实时监控的要求。但由于 3150 神经元芯片只提供 11 个通用 I/O 口,不能满足采集量和控制量要求较多的现场设备的要求,因此研究和开发基于神经元芯片的多点 I/O 的智能节点,是一项有意义的工作。

### 1 NeuronC3150 神经元芯片的特点

NeuronC 芯片既是 Lonworks 技术的核心也是智能节点的核心,目前由 Toshiba 和 Motorola 两家公司生产,主要包括 NeuronC3150 和 NeuronC3120 两种系列。3150 芯片中包括 E²PROM 和 RAM 存储器,同 3120 芯片的区别在于它无内部 ROM,但具有访问外部存储器的接口,寻址空间可达 64 Kbyte。从这一点来说,3150 比 3120 在节点开发上具有更好的灵活性。3150 芯片内部带有 3 个 8 位微处理器:一个用于链路层的控制,另一个用于网络层的控制,第三个用于执行用户的应用程序。该芯片还包含 11 个 I/O 口和完整的 LonTalk 通信协议,它同时具有通信和控制功能。

#### 2 基于神经元芯片智能节点的开发方法

基于神经元芯片开发的智能节点具有结构简单、成本低等优势,其开发方法可分为两种(1)基于控制模块的硬件设计方法。采用这一方法的优势是可缩短产品的开发周期,因为控制模块通常都集成了神经元芯片、Flash 程序存储器、收发器以及 RAM 等 ,用户只需设计自己的应用电路即可完成节点开发。(2)基于收发器的硬件电路设计方法。采用这一方法可以降低节点成本,提高节点的市场竞争力,但是这一方法需要在考虑应用电路设计的同时考虑神经元芯片与 Flash 存储器及RAM 的接口电路,这对于电路板的设计加工及生产工艺的要求都较高。

## 《电子技术应用》2002年第9期

## 3 智能节点的电路设计

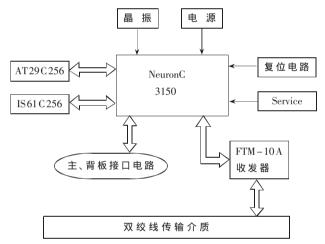

节点采用主、背板结构。主板上集成有控制电路、通信电路和其他附加电路,其结构图如图 1。背板设计为两种多点 I/O 模块(包括多点数字 I/O 模块和多点模拟 I/O 模块)。主、背板之间采用统一标准的 20 针接口。采用主、背板结构设计法,使得此智能节点的应用领域更为广泛,适应性、通用性和功能都大大增强,对于节点应用程序的开发也更为灵活。

图 1 智能节点主板结构图

#### 3.1 主板电路设计

## 3.1.1 控制电路

控制电路主要由神经元芯片,主背板接口电路和片外存储器等组成。各元器件功能如下:

- (1)神经元芯片 采用 Toshiba 公司生产的 3150 芯片, 它主要用于提供对节点的控制、实施与 Lon 网的通信、 支持对现场信息的输入输出等应用服务。

- (2)片外存储器 采用 Atmel 公司生产的 AT29C256 (FLASH 存储器)。 AT29C256 共有 32K 字节的地址空间,其中低 16K 字节空间用来存放神经元芯片的固件(包括 LonTalk 协议等)。高 16 字节空间作为节点应用程序的存储区。采用 ISSI 公司生产的 IS61C256 作为神经元芯片的外部 RAM.。

- (3)主、背板接口电路 用于主板与多点 I/O 模块的电气连接。

#### 3.1.2 通信电路

通信电路的核心——收发器是智能节点与 Lon 网之间的接口。目前 ,Echelon 公司和其他开发商均提供了用于多种通信介质的收发器模块。本智能节点采用 Echelon 公司生产的适用于双绞线传输介质的 FTT-10A 收发器模块。

#### 3.1.3 附加电路

附加电路主要包括晶振电路、复位电路和 Service 电路等。

晶振电路为3150神经元芯片提供工作时钟。

复位电路用于在智能节点上电时产生复位操作。另外,节点还将一个低压中断设备与 3150 的 Reset 管脚相连,构成对神经元芯片的低压保护设计,提高节点的可靠性和稳定性。

Service 电路是专为下载应用程序的电路 ,Service 指示灯对诊断神经元芯片固件状态有指示作用。

#### 3.2 I/O扩展电路设计

3150 神经元芯片包含 11 个通用口 ,用户可根据不同的需求进行灵活配置 ,以便于同外部设备进行接口。对于输入和输出(I/O)数量需求较大的外围设备 ,11 个 I/O 口显然不能满足。虽然可以依靠增加节点数量来满足外围要求 , 但是这样做不仅成本价格高而且增加了安装的工作量 ,维护也不方便。因此 ,通过增加外围电路实现 I/O 扩展 ,成为多点 I/O 智能节点开发的重要部分。I/O 扩展设计包括多点模拟模块设计和多点数字模块设计。

#### 3.2.1 多点模拟模块设计

多点模拟模块主电路图如图 2。TLC2543 是支持 SPI 串行总线的 11 路模拟通道的 12 位逐次逼近型模/数转换器。CS( Pin 15 )片选信号端接 IOO;DATA INPUT( Pin 17 )为串行数据输入,其中四位串行地址用来选择下一个被转换的模拟通道或测试电压寄存器;DATA OUTPUT ( Pin 16 )输出模/数转换的结果; CLK 是维持模/数转换正常工作的时钟。值得注意的是,时钟信号频率较高,任何一点干扰都可能影响模块的正常工作。在 CLK 上串联或并联一支电阻可以起到很明显的抗干扰效果,保证模/数模块的稳定。(本模块中, CLK 接 IO8 ,DATA INPUT 接 IO9 ,DATA OUTPUT 接 IO10 )。TLC2543 还有一个特点:

ANI Hvcc AN0 VCC 19  $\times_{_{108}}$ ANE FOC AN3 18 AN2 CLK 109 AN4 AN<sub>3</sub> DIN AN5 16 1010 AN4 DOUT 47µF AN6 6 15 100 AN5 CS AN7 14 AN6 REF+ AN8 8 13 AN7 REF-AN9 9 12 ANII. ANI0 AN8  $0.1 \mu F$  $0.1 \mu I$ 10 11 ANIO GND 图 2

IO9 输入数据的同时 ,IO10 输出的是上一次模/数转换的值,因此在编写 NeuronC 源程序时要注意模/数转换的时序。选用两支旁路电容 :一支  $47\mu F$  电解电容 ,对低频起滤波作用 ;另一支为  $0.1\mu F$  ,对高频起滤波作用。此模/数模块没有选用电压基准,故在模/数芯片的参考电压边上接了一支  $0.1\mu F$  电容 ,用以去除高频干扰。

#### 3.2.2 多点数字模块设计

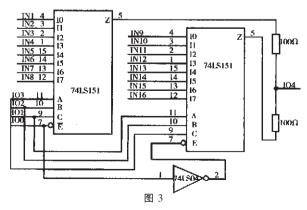

多点数字模块主要包括:输入部分、输出部分、双向 I/O 三部分。通过扩展,模块具有 16 路数字输入通道、15 路数字输出通道和 3 路双向 I/O 通道。

(1)输入部分 采用两片 8 选 1 数据选择器 74LS151 级联, 并将 NeuronC3150 的  $IOO\sim IO3$  定义为 Nibble Output 方式,即半字节输出方式; IO4 定义为 Bit Input 方式,即位输入方式。 $IOO\sim IO3$  作为 16 路输入通道的地址选通信号,与 74LS151 的地址输入端( $\overline{E}$ 、A、B、C 管脚)相连。IO4 作为数字信号入口,与 74LS151 的输出端连接。(具体电路如图 3 )下面的 NeuronC 源程序可完成对 16 路数字通道的定时扫描,定时时间为 1s:

IO\_0 output nibble io\_mselect;//定义半字节输出 IO IO\_4 input bit io\_tmp; // 定义位输入 IO Stimer repeating t\_circle=1;// 定义并初始化定时器 When (timer\_expires(t\_circle))

{ int i ; bit I\_num , temp[15];//定义循环变量通道状态数组初始化通道号

for(i=0;i<16;i++)

{ io\_out(io\_mselect,I\_num) // 写通道号

temp[i]=(io\_in(io\_tmp)==ON)?1:0 )}} // 读通道状态

并存入状态数组

(2)输出部分 如图 4,输出部分由两片 8 位移位寄存器 74LS164 和两片 74LS373 锁存器组成。164 的功能是将 NeuronC I/O 口的 15 位串行帧输出转化为 15 路并行信号输出。373 锁存器的作用是使 164 的 15 路输出在电平转换后加以保持,直至下一次电平转换。为了满足15 路并行输出的要求,在时序上需要使两片 373 严格同步。因此在硬件上增加了非门和 RC 电路,对两片 373 的使能信号加以协调。通过实验,证明此电路能够完全满足设计要求。在 NeuronC 源程序中将 IO8 、IO9 定义为

《电子技术应用》2002年第9期

# 开关电容滤波器的'共振'现象及其对策

镇江江苏大学电气信息工程学院(212013) 陈照章 唐 平 朱湘临

摘 要:分析了开关电容滤波器的"共振"现象及其产生机理。针对该现象提出了解决办法,并结合信号处理仪器系统给出了采用 MAX293 制作抗混滤波器的方案。

关键词:开关电容滤波器 "共振"现象 抗混 编程

在信号处理仪器的硬件系统中抗混滤波器是一重要的部件。根据信号分析的要求,抗混滤波器的截止频率范围控制在 10 Hz~20 kHz。为了提高信号的频率分辨率,要求抗混滤波器的带宽是可变的。比如要分析100 Hz。设计时,按 1、2、4、5 倍乘的原则,将 20 kHz 频率范围分成 14 档不同带宽来处理。若采用一般的模拟低通滤波器必然电路繁复、换档不便、体积太大、不甚以用。而集成开关电容滤波器发展很快,生产公司不少,器件目前已系列化。它改变截止频率非常方便,只要程控不同的采样频率即可。因此,选择 8 阶开关电容椭圆低通滤器 MAX 293 作抗混滤波器,其截止频率后的衰减为

160dB/10 倍频,由文献(1)可知,如截止频率为 1kHz,则到 1.5kHz 处,信号衰减了 80dB<sup>[1]</sup>,接近理想的低通滤波器,这是由椭圆滤波的特点所决定的。实测的波特图(幅频特性)也有相似结果。但在试制过程中,发现该滤波器有"共振"现象,以下就此现象试作分析。

## 1 开关电容滤波器的"共振"现象

在用 NW 1232 低频频率特性测试仪测试 MAX 293 的幅频特性时,发现屏幕上除了预期的幅频特性之外,在采样频率及其整数倍的频率处具有窄带通形状的峰值,其高度达到甚至超过了前面幅频特性平坦部分的最大值。也就是说,当输入信号频率等于采样频率或为采样频率的整数倍时,出现了这一现象。此现象从未见文献报导过,暂时称之为"共振"现象,如在使用中对其不加

Serial Output 方式 ,即串行输出方式。其中 IO8 输出时钟信号,IO9 输出串行数据。IO7 定义为 Bit Output 方式,即位输出方式,作为 164 的清零端。

(3) 双向 I/O 部分 为了使用户对此智能节点的二次开发更为灵活、方便 ,我们在多点数字模块上设计了三个双向 I/O 口 (IO5、IO6、IO10)。用户可根据自己的需

《电子技术应用》2002年第9期

要,利用模块上的拨动开关进行输入、输出切换。

需要注意的是,为了提高智能节点的抗干扰能力, 在输入、输出电路中均采用了光电耦合器进行电气隔 离。特别在输出端加入了三极管功率放大电路以便驱动 外部继电器。

水电厂中的水利机组控制系统中有众多参量需要测量和控制(包括模拟量和数字量),如调速器开关、灭磁信号、主阀开关、冷却水泵、励磁投入信号、锁锭控制等。因此,系统对 I/O 口的需求量较大,传统的智能节点远远不能满足要求。而我们通过对多点 I/O 智能节点的开发,成功地研制出 WSTA 2000 小型水利机组综合自动化装置。此装置已在水电厂中投入使用,运行情况良好。参考文献

- 1 王锦标.现场总线综述. 冶金自动化,1998(6):1

- 2 NodeBuilder User's Guide (Revision 3). Echelon Corporation , 078-0141-01C

- 3 Neuron Chip Data Book. February, 1995

- 4 Neuron C Reference Guide (Revision 2). Echelon Corporation , 078-0141-01B

- 5 Neuron C Programmer's Guide (Revision 4). Echelon Corporation, 078-0141-01D

(收稿日期:2002-04-20)

本刊投稿邮箱:eta@ncse.com.cn 39